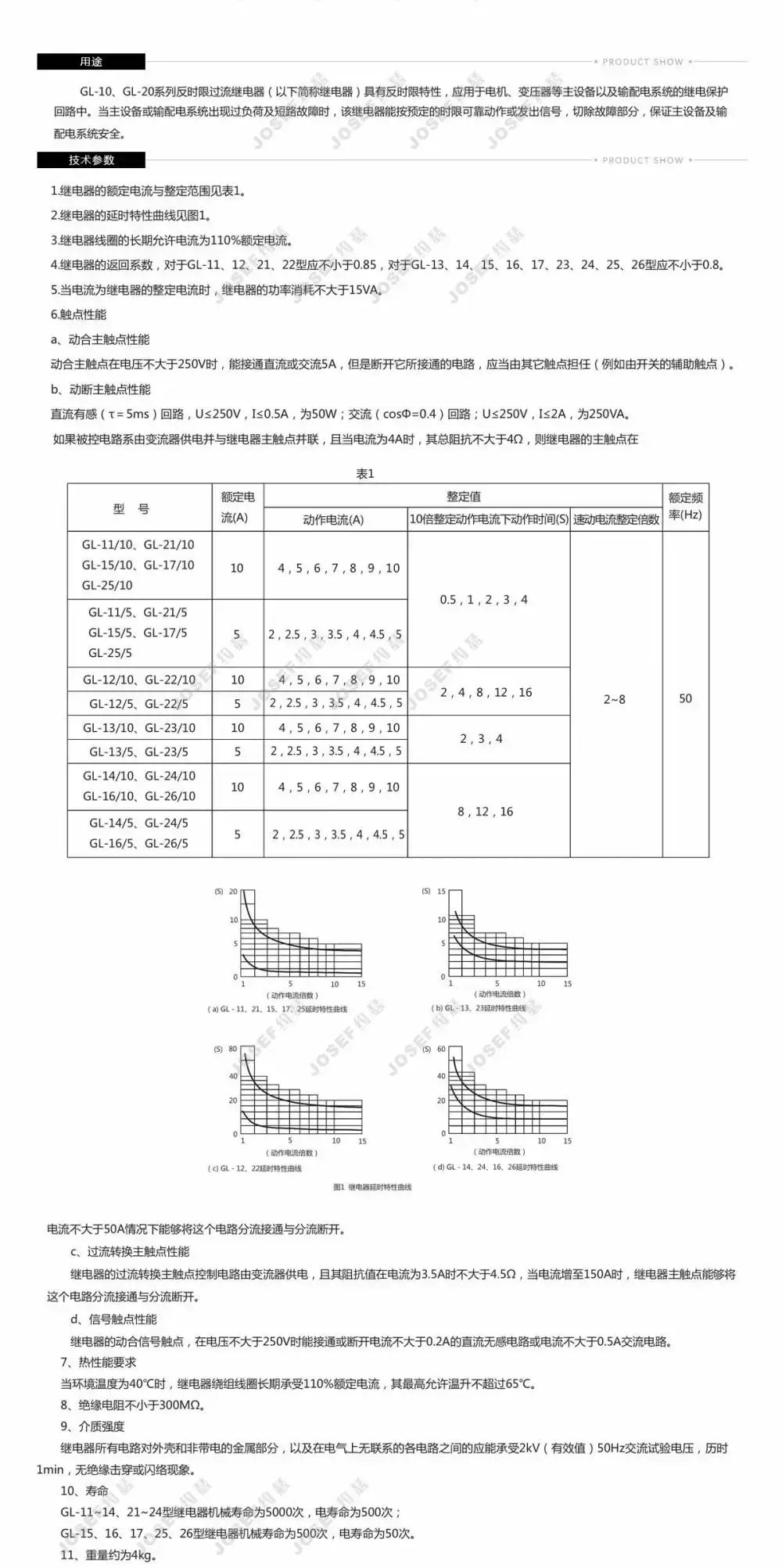

你有沒有遇到這種情況:主控芯片標稱待機電流100μA,軟件也進了深度睡眠,可整機實測靜態(tài)電流卻高出十幾倍?別急著懷疑固件或換芯片——問題很可能出在PCB實現(xiàn)上。這不只是控制邏輯的問題,更是PCB層面的設(shè)計考量:使能信號是否穩(wěn)定?MOS管開關(guān)路徑是否足夠短?斷電后回路會不會通過其他路徑“偷電”?比如某個傳感器的地雖然電源斷了,但信號線還連著主控,形成漏電通路——這種細節(jié),仿真不一定能抓到,只有實測才會暴露。再比如電源域隔離。很多工程師會在原理圖上畫出獨立供電,但在PCB布局時為了布線方便,把多個域的地混在一起鋪銅,結(jié)果域間干擾嚴重,不僅功耗上不去,還影響喚醒穩(wěn)定性。還有DC-DC與LDO的搭配使用。我們見過不少設(shè)計,在主電源用高效DC-DC,卻在后級為圖省事全用LDO穩(wěn)壓,忽略了壓差大時的熱損